模擬集成電路設(shè)計(jì)是現(xiàn)代電子系統(tǒng)的核心,它關(guān)乎信號(hào)的真實(shí)、精確與高效處理。在《模擬集成電路設(shè)計(jì)精粹》的第六章“集成電路設(shè)計(jì)”中,我們將深入探討這一領(lǐng)域的核心概念、設(shè)計(jì)流程與關(guān)鍵技術(shù),揭示從抽象概念到物理實(shí)現(xiàn)的完整路徑。

一、集成電路設(shè)計(jì)概述

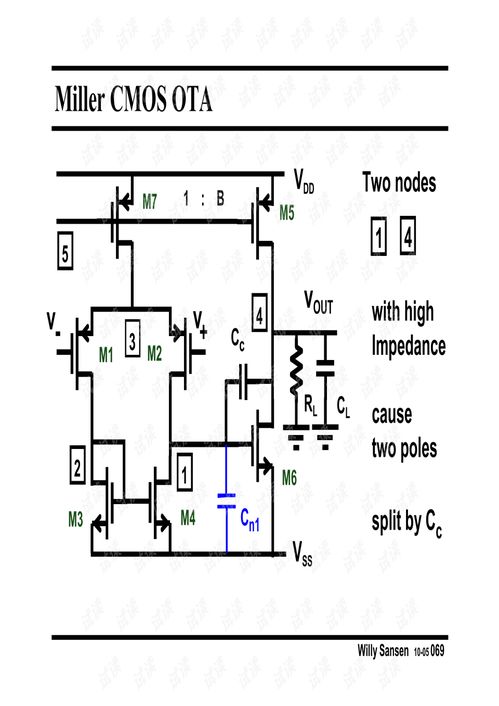

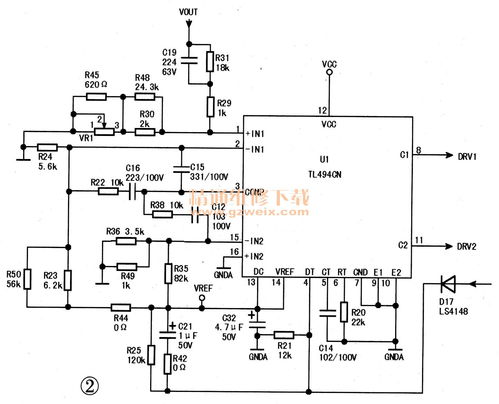

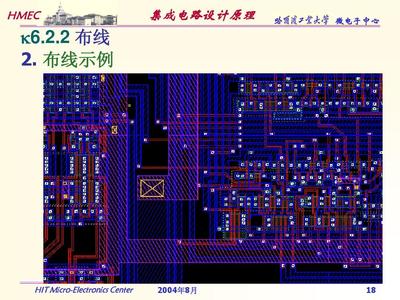

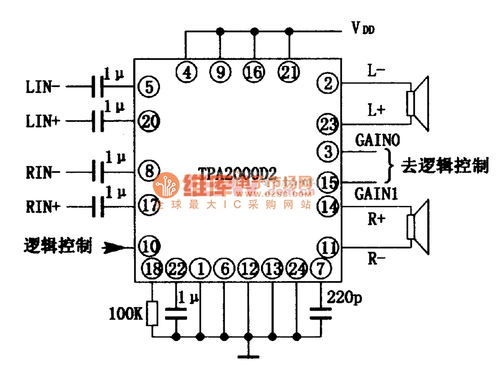

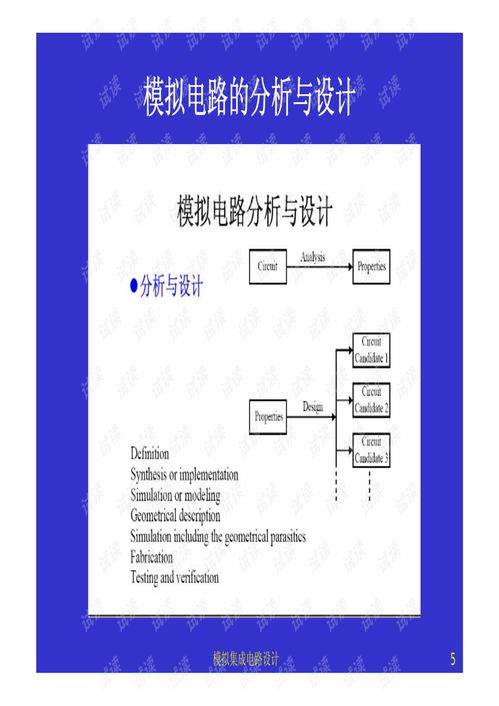

集成電路設(shè)計(jì)是將電路功能、性能指標(biāo)轉(zhuǎn)化為實(shí)際硅芯片版圖的過(guò)程。模擬集成電路設(shè)計(jì)尤其注重性能的優(yōu)化,如增益、帶寬、噪聲、功耗和線性度等。這一過(guò)程通常分為系統(tǒng)級(jí)設(shè)計(jì)、電路級(jí)設(shè)計(jì)、版圖設(shè)計(jì)和驗(yàn)證等階段。系統(tǒng)級(jí)設(shè)計(jì)確定整體架構(gòu)和模塊劃分;電路級(jí)設(shè)計(jì)則聚焦于晶體管級(jí)電路實(shí)現(xiàn),使用SPICE等工具進(jìn)行仿真分析;版圖設(shè)計(jì)是將電路圖轉(zhuǎn)換為物理布局,需考慮匹配、寄生效應(yīng)和可靠性;驗(yàn)證則確保設(shè)計(jì)符合規(guī)格并具備可制造性。

二、關(guān)鍵設(shè)計(jì)原則與技術(shù)

在模擬集成電路設(shè)計(jì)中,幾個(gè)關(guān)鍵原則至關(guān)重要。匹配性是模擬電路性能穩(wěn)定的基礎(chǔ),例如在差分對(duì)或電流鏡中,晶體管的尺寸、布局需高度對(duì)稱以減少工藝偏差影響。噪聲分析不可或缺,因?yàn)槟M信號(hào)易受熱噪聲、閃爍噪聲干擾,設(shè)計(jì)時(shí)需優(yōu)化器件尺寸和偏置以最小化噪聲系數(shù)。電源抑制比和共模抑制比是衡量電路抗干擾能力的重要指標(biāo),通過(guò)采用共源共柵結(jié)構(gòu)、帶隙基準(zhǔn)等技術(shù)可以顯著提升。隨著工藝節(jié)點(diǎn)縮小,短溝道效應(yīng)、漏電流等問(wèn)題日益突出,設(shè)計(jì)者需掌握深亞微米下的建模與補(bǔ)償方法。

三、設(shè)計(jì)流程與工具鏈

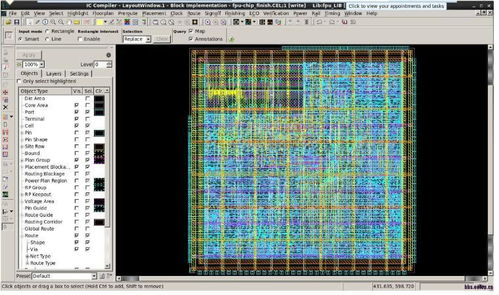

現(xiàn)代集成電路設(shè)計(jì)依賴于成熟的工具鏈。設(shè)計(jì)流程通常以Top-Down方式展開(kāi):從行為級(jí)建模開(kāi)始,使用Verilog-A或MATLAB進(jìn)行系統(tǒng)仿真;進(jìn)而進(jìn)入電路級(jí)設(shè)計(jì),采用Cadence Virtuoso等平臺(tái)繪制原理圖并進(jìn)行DC、AC、瞬態(tài)仿真;版圖階段則使用物理設(shè)計(jì)工具,考慮DRC、LVS規(guī)則檢查,確保制造可行性。寄生參數(shù)提取和后仿真驗(yàn)證是閉環(huán)的關(guān)鍵,以評(píng)估實(shí)際性能。本章還強(qiáng)調(diào)了設(shè)計(jì)復(fù)用和IP核的重要性,它們能加速開(kāi)發(fā)周期,降低成本。

四、挑戰(zhàn)與未來(lái)趨勢(shì)

模擬集成電路設(shè)計(jì)面臨諸多挑戰(zhàn),包括工藝變異性的管理、功耗與性能的權(quán)衡,以及混合信號(hào)集成中的串?dāng)_問(wèn)題。隨著物聯(lián)網(wǎng)、人工智能和5G等應(yīng)用的興起,對(duì)高能效、高集成度模擬電路的需求日益增長(zhǎng)。未來(lái)趨勢(shì)指向更智能的設(shè)計(jì)自動(dòng)化工具,利用機(jī)器學(xué)習(xí)優(yōu)化電路參數(shù);新材料如GaN、SiC的應(yīng)用將拓展高頻、高壓場(chǎng)景下的設(shè)計(jì)邊界。設(shè)計(jì)者需持續(xù)學(xué)習(xí),融合跨學(xué)科知識(shí),以應(yīng)對(duì)不斷演進(jìn)的技術(shù)浪潮。

第六章“集成電路設(shè)計(jì)”不僅是技術(shù)的匯總,更是藝術(shù)與科學(xué)的結(jié)合。它要求設(shè)計(jì)者具備扎實(shí)的理論基礎(chǔ)、豐富的實(shí)踐經(jīng)驗(yàn)和創(chuàng)新的思維模式。通過(guò)掌握這些精髓,我們方能打造出性能卓越、穩(wěn)定可靠的模擬集成電路,推動(dòng)電子技術(shù)向前發(fā)展。