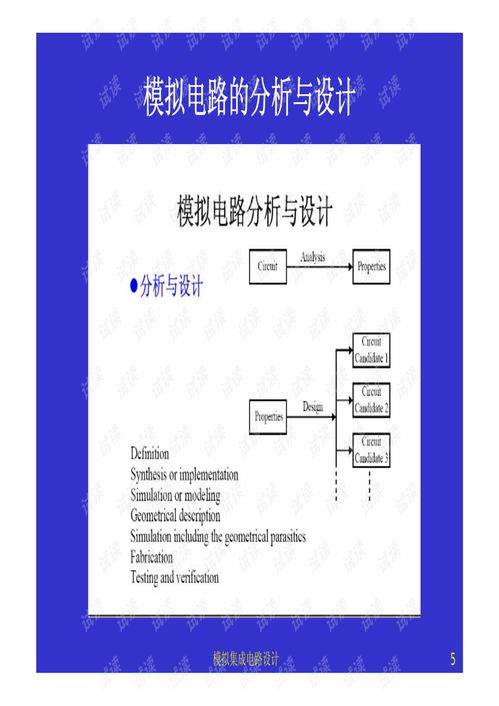

集成電路設計是現代信息產業的基石,其最終物理實現依賴于精密的版圖設計。本文將系統性地介紹從設計概念到物理版圖的完整流程及其關鍵技術。

一、集成電路設計總覽:分層實現之路

集成電路設計是一個典型的自頂向下(Top-Down)過程,通常分為以下幾個層次:

- 系統級設計:定義芯片的整體功能、性能指標和架構。

- 邏輯設計:使用硬件描述語言(如Verilog、VHDL)進行寄存器傳輸級(RTL)設計,實現功能描述。

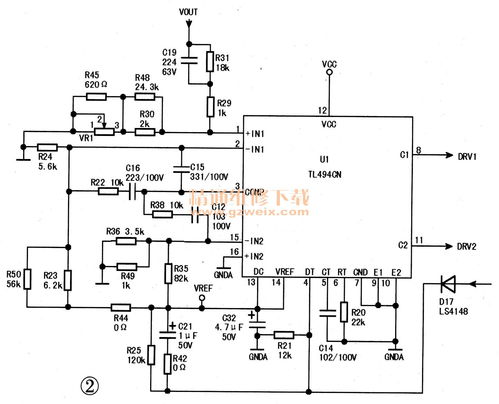

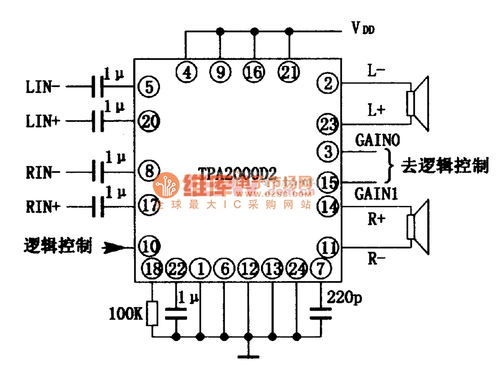

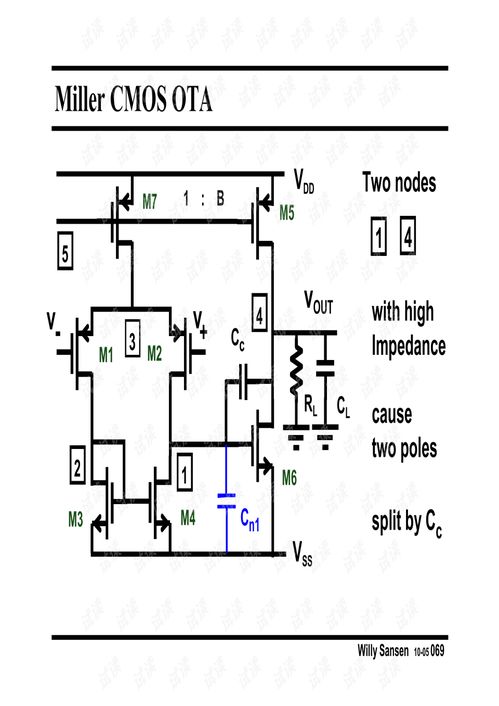

- 電路設計:將邏輯門轉化為晶體管級電路,進行功耗、時序和噪聲的初步分析。

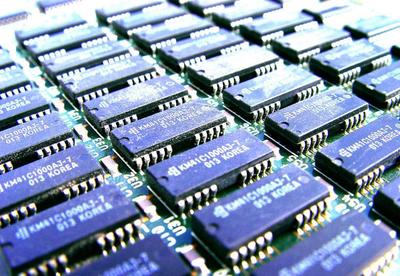

- 物理設計(核心):即版圖設計,將電路圖轉化為可供制造的幾何圖形(版圖),是設計與制造的橋梁。

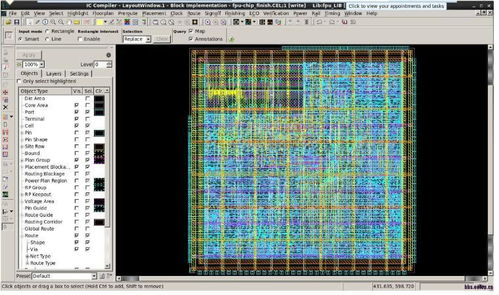

二、版圖設計:物理設計的核心環節

版圖設計是集成電路設計的最后一步,也是決定芯片性能、面積、可靠性和制造成本的關鍵。其主要任務是根據電路原理圖和工藝設計規則,繪制出每一層掩模的幾何圖形。

核心步驟包括:

- 布局:規劃芯片上各個功能模塊(如標準單元、存儲器、模擬模塊)的位置和形狀,優化信號流與互連。目標是減小芯片面積、降低互連延遲和功耗。

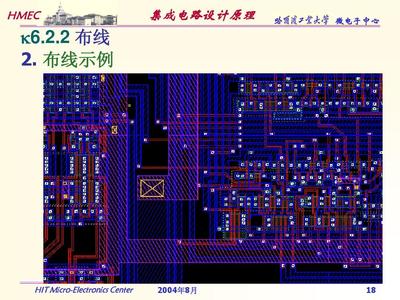

- 布線:在布局確定的模塊之間,根據電氣連接關系,在多個金屬層上完成實際連線的繪制。必須嚴格遵守設計規則,并優化時序、信號完整性和功耗。

- 驗證:確保版圖完全正確,包括:

- 設計規則檢查(DRC):驗證版圖是否符合制造工藝的物理限制(如線寬、間距)。

- 電路圖版圖一致性檢查(LVS):確保繪制的版圖與原始電路圖在電氣連接上完全一致。

- 電氣規則檢查(ERC):檢查潛在的電氣問題,如短路、開路、懸空節點等。

- 寄生參數提取與后仿真:提取版圖中的寄生電阻、電容,進行更精確的時序和功耗分析。

三、關鍵技術挑戰與設計方法

- 深亞微米/納米級效應:隨著工藝節點進入納米尺度,互連延遲主導、功耗密度激增、制造變異增大等問題日益突出。版圖設計必須考慮可制造性設計(DFM)、可靠性設計(DFR)和良率提升。

- 設計自動化(EDA)工具:現代復雜的版圖設計高度依賴EDA工具鏈,包括自動布局布線(APR)、時鐘樹綜合(CTS)、物理驗證等工具,以應對數億晶體管的設計規模。

- 混合信號設計:對于包含模擬/射頻電路和數字電路的芯片,版圖需特別處理噪聲隔離(如保護環、隔離阱)、匹配對稱性及信號完整性等問題。

- 先進封裝協同設計:在系統級封裝(SiP)和芯片異構集成趨勢下,版圖設計需與封裝規劃、硅通孔(TSV)等三維集成技術協同考慮。

四、版圖設計的價值與未來

版圖設計絕非簡單的“繪圖”,而是融合了電路知識、工藝理解、物理效應建模和優化算法的復雜工程。一個優秀的版圖設計師能在給定的約束下,實現性能、功耗、面積和成本的最佳平衡。隨著人工智能與機器學習技術的發展,智能版圖生成與優化正成為新的前沿,有望進一步提升設計效率與芯片質量。

從系統構想到最終掩模,集成電路版圖設計是思想變為現實的最后一環,凝聚了無數工程師的智慧,持續推動著摩爾定律向前演進。